# Tecniche di gestione IO

#### Leonardo Bizzoni

May 16, 2023

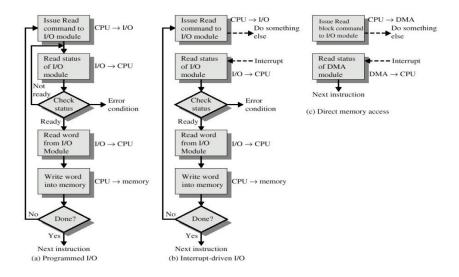

## 1 Programmed I/O

È la metodologia più semplice di gestione dell'input in quanto non fa utilizzo degli interrupt.

Con questa metodologia la periferica assume un ruolo passivo ed è la CPU che si occupa sia del controllo sia del trasferimento dei dati.

Il controllo consiste nell'ispezionare il registro di stato della periferica in attesa che un **ready-bit** assuma un determinato valore per indicare la *prontezza* del trasferimento dei dati. Il <u>processore resta in attesa</u> di riceve il dato.

Da un lato questa metodologia è molto rapida, non appena la CPU riceve il ready-bit richiede subito i dati ed è in grado di memorizzarli in RAM. Dall'altro la CPU è bloccata in uno stato di **busy waiting**.

- Banda passante alta

- Latenza minima

### 2 Interrupt-driven I/O

La periferica segnala alla CPU la necessità di trasferire dei dati tramite l'invio di una interrupt sul bus di sistema(controllo). La CPU dovrà **gestire** questo interrupt, durante una fase di fetch, e finalizzare il trasferimento dei dati.

Questa metodologia è migliore della programmed I/O in quanto la CPU può effettuare altre operazioni non essendo bloccata in busy waiting. Non è la migliore in quanto la CPU dovrà occuparsi di gestire l'interrupt e salvare i dati in memoria.

- Banda passante minore in quanto la gestione dell'interrupt richiede più tempo

- Latenza maggiore a causa della quantità di operazioni per gestire l'interrupt

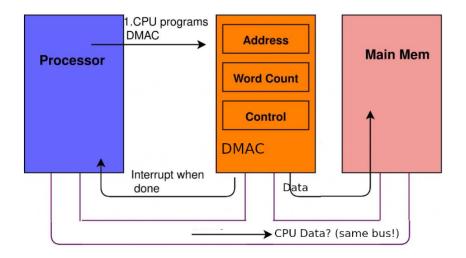

#### 2.1 Direct Memory Access - DMA

Principalmente usato per il rapido trasferimento di grandi quantità di dati. Ogni periferica necessità di 2 registri aggiuntivi:

- un registro che indichi un indirizzo di memoria da dove trasferire/ricevere i dati(Address)

- un registro che indichi la quantità di dati da trasferire(Word Count)

Dato che il DMA ha bisogno di accedere al bus per poter trasferire i dati potrebbe causare problemi se la CPU avesse bisogno di accedere anche'essa al bus. Per risolvere questo problema ci sono 2 strategie:

- attendere che la CPU non utilizzi il bus

- Cycle stealing: alternare il segnale di clock tra processore e DMA

Al termine del trasferimento la periferica segnala alla CPU l'avvenuto trasferimento dei dati tramite l'invio di una interrupt sul bus di sistema(controllo). La CPU risponde all'interrupt riconoscendo l'avvenuto trasferimento.

- $\bullet\,$  Banda passante massima

- Latenza minima