## Esecuzione delle istruzioni

## Leonardo Bizzoni

June 7, 2023

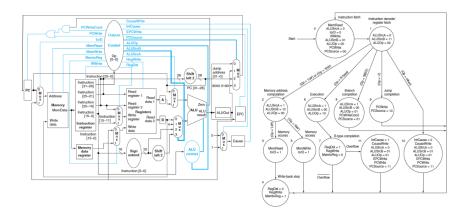

In un datapath multiciclo l'istruzione più corta viene eseguita in 3 cicli di clock uno dedicato alla fetch, uno alla decode e l'ultimo alla execute mentre l'istruzione più lunga viene eseguita in massimo 5 cicli.

- Lo stato **0** rappresenta i segnali che la **Control Unit** deve mandare in output per effettuare l'istruzione di fetch:

- fetch dell'istruzione dalla RAM all'indirizzo indicato dal PC | IR = Mem[PC]

- incremente del PC | PC+=4

- Lo stato 1 rappresenta i segnali che la Control Unit deve mandare in output per effettuare l'istruzione di decode:

- "decodifica" dell'istruzione

- lettura dei registri | A = Reg[IR[25:21]], B = Reg[IR[20:16]]

- calcolo dell'eventuale indirizzo di branch | ALU out = PC+(signExtend(IR[15:0]) << 2)

ullet Gli stati ullet, ullet, ullet, ullet ed i loro nodi figlio rappresentano i segnali per effettuare tutte le possibili istruzione ISA implementato dal nostro datapath